My name is Midhat Feidi. I am a student of senior standing at Montana State University - Bozeman in the Electrical Engineering department. My main contribution to this project is to develop the UART portion of our design.

The UART stands for Universal Asynchronous

Transmit/Receive and is used to transfer data between two pieces of hardware

that have different operating rates. The UART is located in the FPGA, and it

needs to be programmed using Xilinx tools in VHDL. The UART receives data from

the main circuitry, which is also in the FPGA, and transmits it to a computer in

order to display the data in a GUI, a graphical user interface. The data is sent

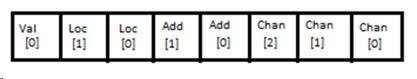

in a package consisting of 8 bits, shown below from least significant bit we

have 3 bits for channel, 2 for address, 2 for location and 1 bit for the value.

We have 8 channels that can be affected by radiation. The address and location

are configured by looking at the memory and figuring out the time of the hit.

The value bit shows if the channel is hit or not by giving a �1� for a hit and a

�0� for a no hit. The data is transferred using an RS-232 cable. The baud rate

on this system is 38400 bit/sec running on a 100MHz clock, which is what the

FPGA�s clock is running at. The UART was first programmed to receive from the

bit switch on the board. The bit switch sends in ASCII code through the cable

and the bit shows up on a hyper terminal window. Then, another part of the code

is set to transmit from the computer to the board. The final test for the UART

was after downloading the transmit and receive codes, and pushing a letter on

the keyboard of the computer will go through the cable and the board and then

comes back up to the computer and shows up on the hyper terminal window. This

concludes that the UART is functioning correctly.

Packet

Format